# CD54ACT00, CD74ACT00 QUADRUPLE 2-INPUT POSITIVE-NAND GATES

SCHS308B - JANUARY 2001 - REVISED JUNE 2002

- Inputs Are TTL-Voltage Compatible

- Speed of Bipolar F, AS, and S, With Significantly Reduced Power Consumption

- Balanced Propagation Delays

- ±24-mA Output Drive Current

- Fanout to 15 F Devices

- SCR-Latchup-Resistant CMOS Process and Circuit Design

- Exceeds 2-kV ESD Protection Per MIL-STD-883, Method 3015

#### CD54ACT00...F PACKAGE CD74ACT00 . . . E OR M PACKAGE (TOP VIEW) 14 🛮 V<sub>CC</sub> 1A 1B 🛮 2 13 **[**] 4B 1Y 🛮 3 12 🛮 4A 2A 🛮 4 11 **[**] 4Y 2B 🛮 5 10 3B 9 ∏ 3A 2Y 6 GND 7 8 3Y

### description

The 'ACT00 devices contain four independent 2-input NAND gates. Each gate performs the Boolean function of  $Y = \overline{A} \cdot \overline{B}$  or  $Y = \overline{A} + \overline{B}$  in positive logic.

#### ORDERING INFORMATION

| TA             | PACKAGE† |               | ORDERABLE<br>PART NUMBER | TOP-SIDE<br>MARKING |

|----------------|----------|---------------|--------------------------|---------------------|

|                | PDIP – E | Tube          | CD74ACT00E               | CD74ACT00E          |

| _55°C to 125°C | SOIC - M | Tube          | CD74ACT00M               | ACT00M              |

| -55 C to 125 C | 301C - W | Tape and reel | CD74ACT00M96             | ACTOON              |

|                | CDIP – F | Tube          | CD54ACT00F3A             | CD54ACT00F3A        |

<sup>†</sup> Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are available at www.ti.com/sc/package.

## FUNCTION TABLE (each gate)

| INP | UTS | OUTPUT |

|-----|-----|--------|

| Α   | В   | Υ      |

| Н   | Н   | L      |

| L   | X   | Н      |

| Х   | L   | Н      |

logic diagram, each gate (positive logic)

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SCHS308B - JANUARY 2001 - REVISED JUNE 2002

### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage range, V <sub>CC</sub>                                                                        | –0.5 V to 6 V    |

|--------------------------------------------------------------------------------------------------------------|------------------|

| Input clamp current, $I_{ K }(V_{ } < 0 \text{ or } V_{ } > V_{CC})$ (see Note 1)                            | ±20 mA           |

| Output clamp current, I <sub>OK</sub> (V <sub>O</sub> < 0 or V <sub>O</sub> > V <sub>CC</sub> ) (see Note 1) | ±50 mA           |

| Continuous output current, I <sub>O</sub> (V <sub>O</sub> = 0 to V <sub>CC</sub> )                           | ±50 mA           |

| Continuous current through V <sub>CC</sub> or GND                                                            | ±100 mA          |

| Package thermal impedance, θ <sub>JA</sub> (see Note 2): E package                                           | 80°C/W           |

| M package                                                                                                    | 86°C/W           |

| Storage temperature range, T <sub>stg</sub>                                                                  | . −65°C to 150°C |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### recommended operating conditions (see Note 3)

|             |                                    | T <sub>A</sub> = 25°C |     |     | –40°C TO<br>85°C |     | –55°C TO<br>125°C |      |

|-------------|------------------------------------|-----------------------|-----|-----|------------------|-----|-------------------|------|

|             |                                    | MIN                   | MAX | MIN | MAX              | MIN | MAX               |      |

| Vcc         | Supply voltage                     | 4.5                   | 5.5 | 4.5 | 5.5              | 4.5 | 5.5               | V    |

| VIH         | High-level input voltage           | 2                     |     | 2   |                  | 2   |                   | V    |

| $\vee_{IL}$ | Low-level input voltage            |                       | 0.8 |     | 0.8              |     | 0.8               | V    |

| VI          | Input voltage                      | 0                     | VCC | 0   | VCC              | 0   | VCC               | V    |

| ٧o          | Output voltage                     | 0                     | VCC | 0   | VCC              | 0   | VCC               | V    |

| ІОН         | High-level output current          |                       | -24 |     | -24              |     | -24               | mA   |

| loL         | Low-level output current           |                       | 24  |     | 24               |     | 24                | mA   |

| Δt/Δν       | Input transition rise or fall rate |                       | 10  |     | 10               |     | 10                | ns/V |

NOTE 3: All unused inputs of the device must be held at V<sub>CC</sub> or GND to ensure proper device operation. Refer to the TI application report, Implications of Slow or Floating CMOS Inputs, literature number SCBA004.

# electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| PARAMETER      | TEST CONDITIONS                  |                                      | VCC            | T <sub>A</sub> = 25°C |      | –40°C TO<br>85°C |      | –55°C TO<br>125°C |      | UNIT |

|----------------|----------------------------------|--------------------------------------|----------------|-----------------------|------|------------------|------|-------------------|------|------|

|                |                                  |                                      |                | MIN                   | MAX  | MIN              | MAX  | MIN               | MAX  |      |

|                |                                  | ΙΟΗ = -50 μΑ                         | 4.5 V          | 4.4                   |      | 4.4              |      | 4.4               |      |      |

| Vo.,           | W W 27W                          | I <sub>OH</sub> = -24 mA             | 4.5 V          | 3.94                  |      | 3.8              |      | 3.7               |      | ٧    |

| VOH            | VI = VIH or VIL                  | $I_{OH} = -50 \text{ mA}^{\ddagger}$ | 5.5 V          |                       |      |                  |      | 3.85              |      |      |

|                |                                  | $I_{OH} = -75 \text{ mA}^{\ddagger}$ | 5.5 V          |                       |      | 3.85             |      |                   |      |      |

|                |                                  | I <sub>OL</sub> = 50 μA              | 4.5 V          |                       | 0.1  |                  | 0.1  |                   | 0.1  | _    |

| V              | \\. = \\ or \\.                  | I <sub>OL</sub> = 24 mA              | 4.5 V          |                       | 0.36 |                  | 0.44 |                   | 0.5  |      |

| VOL            | $V_I = V_{IH}$ or $V_{IL}$       | $I_{OL} = 50 \text{ mA}^{\ddagger}$  | 5.5 V          |                       |      |                  |      |                   | 1.65 | V    |

|                |                                  | I <sub>OL</sub> = 75 mA <sup>‡</sup> | 5.5 V          |                       |      |                  | 1.65 |                   |      |      |

| lį             | $V_I = V_{CC}$ or GND            |                                      | 5.5 V          |                       | ±0.1 |                  | ±1   |                   | ±1   | μΑ   |

| Icc            | $V_I = V_{CC}$ or GND,           | I <sub>O</sub> = 0                   | 5.5 V          |                       | 4    |                  | 40   |                   | 80   | μΑ   |

| ΔlCC           | $V_{I} = V_{CC} - 2.1 \text{ V}$ |                                      | 4.5 V to 5.5 V |                       | 2.4  |                  | 2.8  |                   | 3    | mA   |

| C <sub>i</sub> |                                  |                                      |                |                       | 10   |                  | 10   |                   | 10   | pF   |

<sup>‡</sup> Test one output at a time, not exceeding 1-second duration. Measurement is made by forcing indicated current and measuring voltage to minimize power dissipation. Test verifies a minimum 50-Ω transmission-line drive capability at 85°C and 75-Ω transmission-line drive capability at 125°C.

NOTES: 1. The input and output voltage ratings may be exceeded if the input and output current ratings are observed.

<sup>2.</sup> The package thermal impedance is calculated in accordance with JESD 51-7.

# CD54ACT00, CD74ACT00 QUADRUPLE 2-INPUT POSITIVE-NAND GATES

SCHS308B - JANUARY 2001 - REVISED JUNE 2002

### **ACT INPUT LOAD TABLE**

| INPUT  | UNIT LOAD |

|--------|-----------|

| A or B | 0.15      |

Unit load is  $\Delta I_{CC}$  limit specified in electrical characteristics table (e.g., 2.4 mA at 25°C).

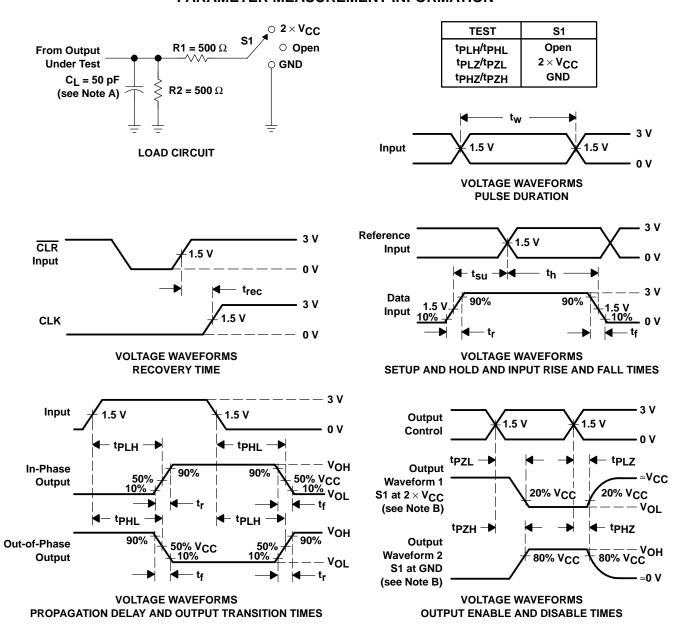

# switching characteristics over recommended operating free-air temperature range, $V_{CC}$ = 5 V $\pm$ 0.5 V, $C_L$ = 50 pF (unless otherwise noted) (see Figure 1)

| PARAMETER        | FROM<br>(INPUT) | I TO I    |     | -40°C TO -55°C TO<br>85°C 125°C |     |      | UNIT |

|------------------|-----------------|-----------|-----|---------------------------------|-----|------|------|

|                  | (IIVI O1)       | (5511 51) | MIN | MAX                             | MIN | MAX  |      |

| <sup>t</sup> PLH | A or B          | V         | 3.4 | 9.5                             | 3.2 | 10.8 | ns   |

| t <sub>PHL</sub> | AUID            | ī         | 2.8 | 8                               | 2.7 | 13.2 |      |

### operating characteristics, $V_{CC}$ = 5 V, $T_A$ = 25°C

|                 | PARAMETER                     |    | UNIT |

|-----------------|-------------------------------|----|------|

| C <sub>pd</sub> | Power dissipation capacitance | 45 | pF   |

#### PARAMETER MEASUREMENT INFORMATION

NOTES: A. C<sub>I</sub> includes probe and test-fixture capacitance.

- B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

- C. All input pulses are supplied by generators having the following characteristics: PRR  $\leq$  1 MHz,  $Z_O = 50 \Omega$ ,  $t_r = 3 \text{ ns}$ ,  $t_f = 3 \text{ ns}$ . Phase relationships between waveforms are arbitrary.

- D. For clock inputs, f<sub>max</sub> is measured with the input duty cycle at 50%.

- E. The outputs are measured one at a time with one input transition per measurement.

- F. tpLH and tpHL are the same as tpd.

- G. tpzL and tpzH are the same as ten.

- H. tpLz and tpHz are the same as tdis.

Figure 1. Load Circuit and Voltage Waveforms

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third—party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265

Copyright © 2002, Texas Instruments Incorporated